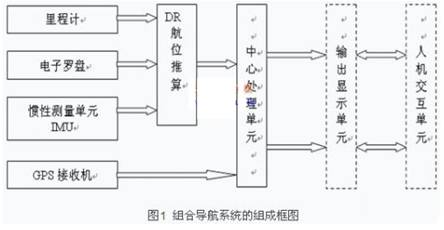

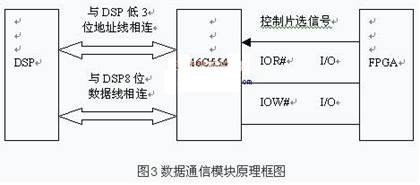

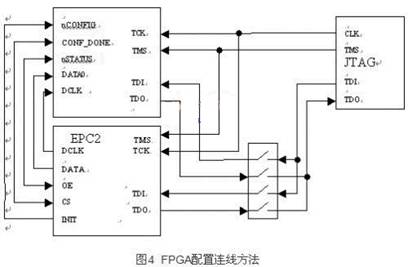

Hardware Design of Vehicle GPS/DR Integrated Navigation System Based on DSP This article refers to the address: http:// Aiming at the development of low-cost integrated navigation technology, combined with the characteristics of main sensors, this paper introduces the design of the GPS/DR integrated navigation system with the floating point DSPTMS320VC33 as the integrated navigation algorithm and the communication port expansion using TL16C554. The design method of the system hardware is out. The designed system has the characteristics of small size, low cost, good real-time performance, high reliability and good expandability, and has wide application value. 0 Preface At present, the accuracy of differential GPS horizontal positioning has reached 3~5m, which fully meets the requirements of vehicle positioning accuracy. However, GPS signal occlusion problems often occur in high-rise buildings in cities or through overpasses, resulting in GPS not being properly positioned. Dead reckoning (DR) is a commonly used vehicle positioning technology, but the direction sensor accumulates errors over time and cannot be used alone or for a long time. The integrated navigation system can use the position and velocity information provided by the GPS system to correct and compensate the error of the DR system in real time. When the GPS signal is out of lock, the dead reckoning can be completed by the DR system, which improves the reliability of the integrated navigation system. Sex. In addition to a large number of arithmetic processing tasks, the integrated navigation system also implements functions such as data acquisition of inertial measurement units IMU (gyroscope and accelerometer) and GPS sensors, communication with external systems, sequential logic control, and human-machine interface. In this case, if only one DSP chip is used, the real-time performance of the system is poor, so most combined systems use two or more DSPs or one or several general-purpose microprocessors MPU plus a DSP. A scheme that constitutes a master-slave multiprocessor system. At present, the combination of DSP and FPGA to process high-speed digital signals is increasingly used. 1 GPS / DR integrated navigation system The GPS/DR combination system has the functions of receiving and processing odometer information, electronic compass information, inertial measurement unit IMU and GPS information, and the main block diagram of the system composition is shown in FIG. 1 . The absolute position information provided by the GPS can provide the initial value of the estimated positioning for the DR and perform error correction; on the other hand, the estimation result of the DR can be used to compensate the random error in the partial GPS positioning, thereby smoothing the positioning trajectory. Therefore, by combining the two systems with appropriate methods and making full use of the complementarity of their positioning information, it is possible to obtain higher positioning accuracy and reliability than when using either method alone [1]. 2 the composition of the central processing unit At present, the navigation system has developed into an integrated navigation system using multi-sensor data fusion. The navigation computer has to perform a large amount of data communication while completing complex calculations. Therefore, it must have a rich communication interface to complete the task of collecting and transmitting sensor data. This requires the central processing unit to be able to communicate with the outside while ensuring computational accuracy and computational speed. Through the functional analysis of the system, the navigation computer needs to complete data acquisition, data processing and data output functions. The data input part mainly completes the collection of various sensor output data; the data processing part mainly completes the data filtering, the error compensation and initial alignment of the micro inertial measurement component, the Kalman filter, and the navigation parameter calculation; the data output part is mainly responsible for Navigation parameter output, used for positioning navigation or the input required in the next step. Due to the use of multiple sensors for information fusion, more peripheral communication interfaces are required. At the same time, external sensor data output communication is mainly performed through an asynchronous serial communication port conforming to the RS-232 standard. If it is directly connected to the central processing unit, a large number of interruptions are made. The response will definitely affect the processing speed of the CPU. Currently, the serial port resources that various MCUs and MPUs can provide are limited. Many of the traditional designs use the PC104 as the central processor of the system. The PC104 is large and expensive, which is not conducive to the miniaturization, low power consumption and low cost of the system. Therefore, this design considers the DSP+FPGA+TL16C554 scheme for design, in which DSP completes the main navigation parameter calculation, uses TL16C554 to expand the external communication interface, FPGA completes the serial port simulation and corresponding logic control to ensure the three Improve the operating efficiency and accuracy of the system through high-speed communication of data lines. The core processor of the central processing unit has to perform large-scale matrix operations and algebraic operations, so the system uses the floating-point DSP chip TMS320VC33. The chip has an operating speed of 150 MFLOPS and 75 MIPS with a single instruction cycle of 13 ns. The TMS320VC33 increases speed by improving hardware capabilities, while other processors increase speed by improving software functionality or coding speed. This way of improving performance through hardware is not possible on previous single-chip DSPs. The processor has the powerful ability to perform parallel multiplication arithmetic on integer and floating point data in a single cycle. At the same time, the chip has the characteristics of low power consumption and low cost, which meets the design requirements of the system [2]. The FPGA has programmable features that make it easy to perform the logic we need. The FPGA is used to extend the peripheral communication interface, mainly to extend the TTL level serial communication port as a backup for the system. Based on the resource requirements for serial communication and future expansion, ALTERA's ACEX1K30 (hereinafter referred to as ep1k30) is used to complete this work. Ep1k30 can provide 119000 resources, with 1728 logic macro units, can realize UART serial port, and at the same time can complete the corresponding decoding, logic control and other functions [3]. The system contains multiple sensors, which requires the processor to expand multiple serial ports. The DSP chip TMS320VC33 itself has a serial communication port. If serial communication is directly used on the serial port resources of the DSP chip, it is only suitable for occasions where the transmission data is relatively small and the transmission rate is slow. [] The software programming is complicated, and the serial communication is controlled. It takes a lot of system resources and affects the real-time processing function of the sensor. Therefore, the system uses TI's 4-channel asynchronous transceiver integrated chip TL16C554 to extend the DSP serial port to realize communication between the sensor and the navigation computer. The chip is a type that has serial asynchronous communication. The large-scale integrated circuit chip of the interface can realize the parallel/serial, serial/parallel conversion function of data. It has a 16-byte FIFO buffer inside. In FIFO mode, data is buffered to 16-byte packets before transmission and reception, reducing the number of CPU interrupts. The internal contains 4 modified 16C550 asynchronous transfer devices, making serial I / O more reliable [5]. The overall hardware design block diagram of the central processing unit is shown in Figure 2. The system fully utilizes the advantages of DSP for adding and multiplying operations, realizing the real-time operation of navigation parameters, and using FPGA and 16C554 to extend the peripheral communication interface, converting serial data into parallel data and communicating with DSP through data bus, processing The device is freed from a large amount of I/O interrupt response burden, improving the operating efficiency of the CPU. The calculated navigation parameters are then converted to the serial data format through the data bus to the FPGA. At the same time, considering that the IMU data volume is large, the data update rate is greater than 100 Hz, and each received packet data is not directly sent to the DSP, but the filter processing is first performed, and then the data is temporarily stored through a FIFO. When the amount of data reaches a certain level, the DSP is notified to take the data away. This can further reduce the burden on the DSP and improve the operating efficiency. 3 central processing unit hardware design The hardware part of the central processing unit is mainly composed of a power module, a data communication module, an FPGA part, a DSP part, and the like. 3.1 system power module The entire system requires four voltages of 1.8V, 2.5V, 3.3V, and 5V. The DSP needs 1.8V and 3.3V as the core power supply and I/O power supply; the FPGA needs 2.5V and 3.3V voltage supply; the GPS needs 5V voltage supply, so the whole system uses 5V voltage supply. Then, through two pieces of TI's TPS73HD3XX series chip for voltage conversion, the required voltage can be obtained separately. The TPS73HD3XX series of chips are dual voltage output conversion chips with very low quiescent current. Even for varying loads, the quiescent current can remain unchanged in practice. 3.2 data communication module The hardware structure of the TL16C554 extended data communication module is shown in Figure 3. The address lines A2 to A0 and the data lines D7 to D0 of the TL16C554 are directly connected to the address bus A2 to A0 of the DSP and the external data lines D7 to D0, respectively, and the chip select signals CSA~CSD, the read/write signals IOR/IOW, and the interrupt signal INTA. ~INTD is connected to the FPGA and processed by the FPGA. The FPGA can be used to flexibly configure the address of the UART on the one hand, and can also flexibly generate the strobe and read and write signals of the UART on the other hand, thereby enhancing the flexibility of the system and facilitating system debugging. 3.3 FPGA section The traditional system design is mostly a multi-machine parallel system in which the DSP is the host responsible for data processing and the microcontroller is the slave responsible for data acquisition. However, the speed limitation of the slave single-chip microcontroller restricts the speed of the entire acquisition processing system. In response to this situation, the traditional multi-machine structure is changed to the host-type stand-alone structure: the system still uses the DSP as the data processing host, and replaces the past slave system with a pure hardware subsystem composed of various counters, logic circuits and clock circuits. [4]. However, if the traditional method is adopted, that is, using a standard digital circuit chip to extend the implementation of this subsystem, a plurality of circuit chips are inevitably required, which not only makes the system structure complicated, but also increases the number of connections, and also reduces the reliability. Therefore, the system uses a field programmable gate array device FPGA to design the subsystem. The biggest advantage of designing this system with FPGA is that it saves PCB board area and meets the requirements of low cost. And after the system design is completed, if you want to upgrade and improve the system, you don't have to change any hardware circuits, just reprogram the FPGA internal logic. After the FPGA is powered off, the configuration information cannot be saved. If it is powered on again, it needs to be reconfigured. Therefore, you need to use off-chip memory to save the configuration information. In this design, ALTERA's epc2 is selected as the configuration chip. Epc2 is a programmable FLASH memory that can be erased multiple times, specifically for the configuration of ALTERA's FPGA. At the same time, the JTAG port on the system board can be used to program epc2 and configure the FPGA online. The online configuration of the FPGA and the programming of the epc2 are switched by the DIP switch. The specific hardware connection is shown in Figure 4. 3.4 DSP part DSP needs system algorithm program memory, using FLASH memory for storage. This system uses four 256k×16bCY7C1041 to expand two 256k×32b RAMs, which provides storage space for complex combination algorithm; two 16-bit SST39VF400FLASH chips are selected as the system. Program memory. The use of FLASH memory overcomes the disadvantages of the large size of the conventional EPROM, and at the same time helps to reduce the area of ​​the circuit board. Through the DSP emulator, according to the FLASH programming algorithm, the program can be written into the FLASH to complete the storage of the DSP algorithm. When the system is powered on, it can be loaded quickly by bootstrapping. Doing so reduces the cost, size, and power consumption of the system. Add a FIFO before the DSP, wait for the data to meet the requirements and then read it together by the DSP, thereby solving the problem that the IMU output data volume is large and the CPU response is frequent. Optimized system efficiency. Each data in the IMU data consists of two parts: high byte and low byte. After receiving data through the serial port, it can be combined into a 16-bit form. The 16C554 chip has a 16-byte FIFO buffer to meet system requirements. The half full signal of the FIFO is used as an interrupt signal for notifying the DSP to receive data, and the DSP is notified to read. According to the overhead time of the data read and write by the DSP and the amount of calculation performed, and considering the size of the actual received data and the transmission baud rate, calculate the time taken by the DSP to perform a packet of data and the cost of writing a packet of data in the FIFO. Time, so that the system can successfully complete the solution task. 4 Conclusion The GPS/DR vehicle combination positioning navigation system combines the GPS system with the DR system to improve the system's effectiveness, integrity and accuracy. The DR track estimation system can ensure the vehicle position information output when the satellite signal is lost. The system has all-round, all-weather, unobstructed and high-precision features, and has a good application prospect. The integrated navigation system has powerful data processing capabilities, and has the advantages of small size, low cost, high reliability, and good real-time performance. The design fully utilizes the powerful data processing capability of DSP, and takes advantage of the high integration programming of FPGA, which is convenient and fast, and makes the system have much room for improvement in the future. It can realize different functions with the same hardware. . Liquid Crystal Display,Lcd Screen Displays,Calculator Lcd Display,Lcd Display For Car Bluetooth Dongguan Yijia Optoelectronics Co., Ltd. , https://www.everbestlcdlcm.com