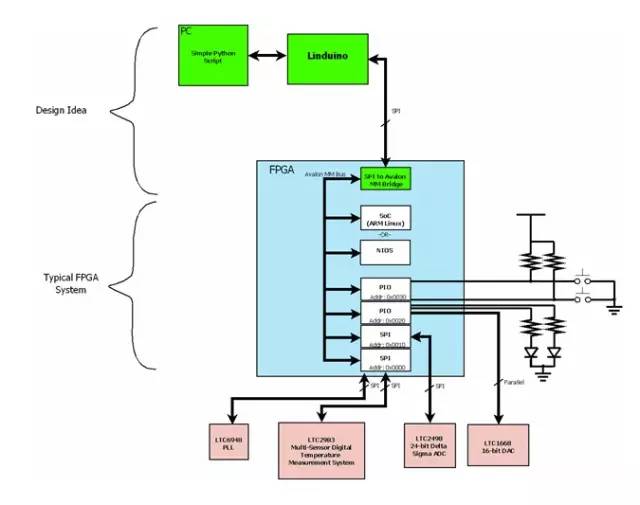

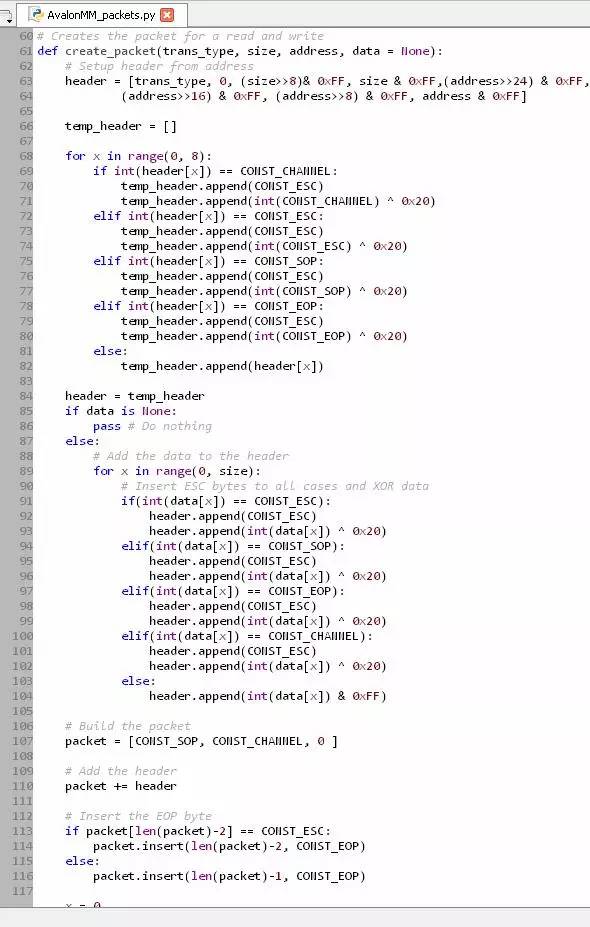

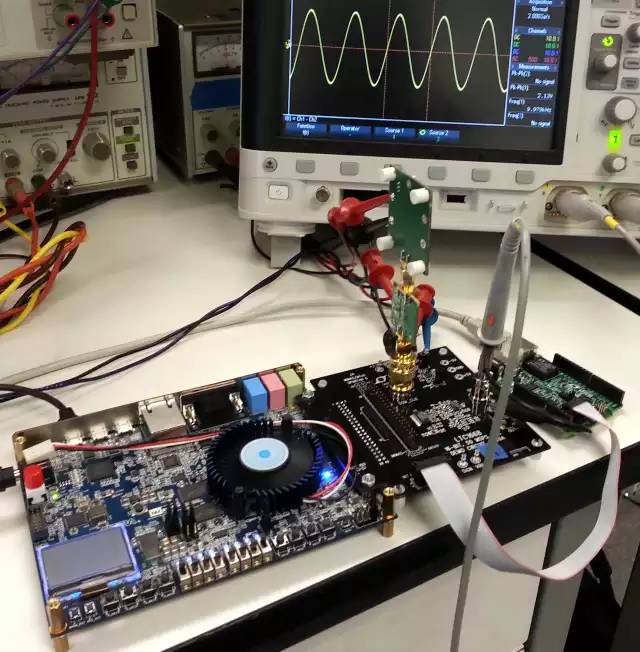

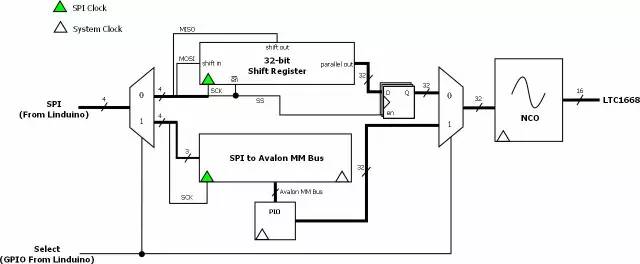

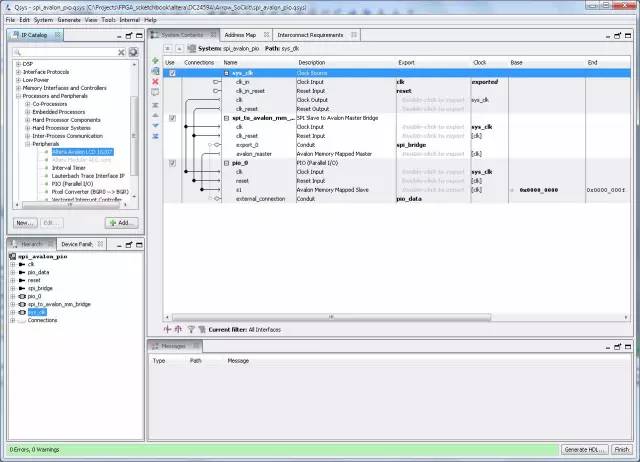

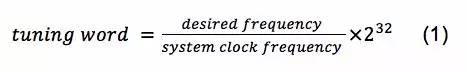

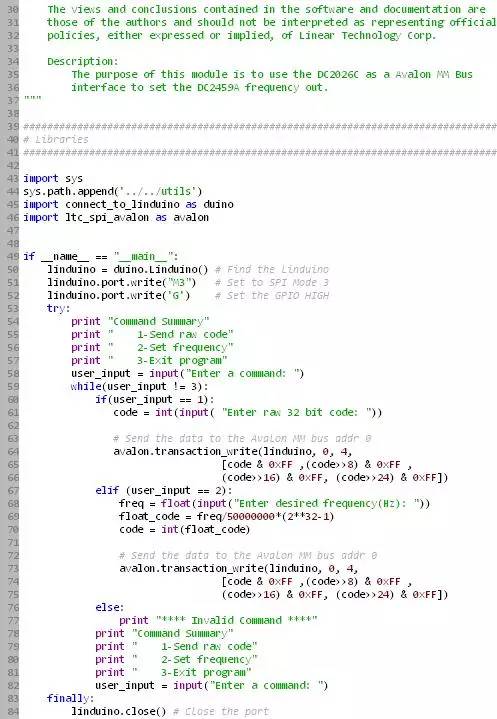

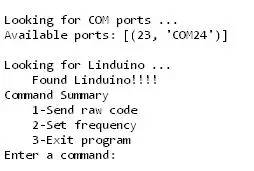

Many FPGA designs use embedded processors for control. The typical solution is to use a soft processor such as the Nios, although FPGA SoCs with hard processors have become popular. Figure 1 shows a typical Altera FPGA system that includes a processor and various peripherals connected through Altera's Avalon Memory Map (MM) bus. These processors greatly simplifies end-applications, but require a strong programming background and sophisticated toolchain knowledge. This will hinder debugging, especially when hardware engineers do not want to turn to software engineers and only need a simple way to read and write peripherals. Figure 1: Typical Altera FPGA system connected using the Avalon memory-mapped bus. This design example uses Altera's SPI Slave to Avalon MM bridge to implement a simple method of hooking up to the Avalon bus. This technique has two advantages: it does not affect the original system design, and the bridge can co-exist with the embedded processor. For the system shown in Figure 1, this SPI bridge allows engineers to directly control the frequency of the LTC6948 fractional-N PLL, set the voltage of the LTC1668 digital-to-analog converter, read the voltage of the LTC2498 analog-to-digital converter, or read the LTC2983 The temperature is just like a processor. Figure 2: Highlights + Example Code + Reverse Engineering = Python script. Altera provides a reference design for the SPI-Avalon MM bridge. Unfortunately, there are very few related documents and the Nios processor is used as the SPI master. This actually violates the original intention of using the SPI bridge, because Nios can directly connect to the Avalon MM bus. The practical SPI master is Linear Technology's Linduino microcontroller, which is a clone of the Arduino processor, but adds additional features such as an interface to the LT demo board. One of the additional features is the level translation SPI port. This level shifting feature is especially useful when connecting FPGA I/O groups with voltages as low as 1.2V. The Linduino firmware can be used to accept commands from a virtual COM port and translate commands into SPI processing. After reverse engineering the Altera design example (Figure 2), a Python library can be obtained, and then the data packets acceptable to the SPI bridge can be created. These packets are then translated into Linduino commands. The Python script then allows the hardware engineer to fully control the entire project without redeveloping the interface protocol. The LinearLabToolsPhython folder provides examples of Python scripts that help the LTC1668 digital-to-analog converter control the frequency of the digital pattern generator. Figure 3 shows the demonstration device. Figure 3: DC2459 digital-to-analog converter demo board (right) inserted into the FPGA board (left). Figure 4 shows the system block diagram. Note that the digitally controlled oscillator (NCO) can be controlled by a shift register or PIO core. The shift register is used for debugging because it can directly control the NCO. Setting the GPIO line high activates the SPI-Avalon bridge, which in turn controls the 32-bit PIO port on the Avalon bus. The PIO output is then used to control the NCO frequency. Figure 4: FPGA system block diagram. With some basic system operations, additional peripheral cores can be connected to the bus. To help with system design, Altera provided a tool called Qsys that provides a graphical user interface (GUI) for connecting to various IPs. Qsys can translate the GUI design system (Figure 5) into HDL. Peripheral addresses are fully configurable. In this case, PIO is set to base address 0x0. Figure 5: Qsys GUI. After the design is implemented in the FPGA, the two functions included in the Python library provided by LinearLabTools can be connected to the design: Transaction_write(dc2026, base, write_size, data) transaction_read(dc2026, base, read_size) The first parameter of these functions is Linduino's serial port instance. The second parameter is the peripheral address on the Avalon bus. These two functions are used to receive and return byte lists, respectively. Both functions have some flexibility when reading and writing IP. In order to set the NCO for a given example, only transaction_write is required. Equation 1 is used to determine the adjustment word. To set the NCO to 1kHz and have a 50MSPS sampling rate, the value of the adjustment word needs to be set to 85899 or 0x00014F8B and transmitted in 4 bytes together. Thus, the Python code that sets the DAC to 1 kHz is: transaction_write(linduino_serial_instance, 0, 0, [0x0, 0x01, 0x4F, 0x8B]) Figure 6: Python Avalon bus example. The Python script in Figure 6 describes a simple text interface for configuring the NCO. It is worth mentioning that the SPI bridge uses SPI mode 3. This was determined through continuous trial and error, and was determined after analyzing the SPI interface of the Nios processor in the Altera example. This design example provides a way to control the system without using an embedded processor. It can help hardware engineers get a project without disturbing the software engineer, and has minimal impact on the hardware design. Orange Enzyme Into Beauty Revitalizing Mask 2

Remove dirt and excess oil within the pores, and remove aging skin, making skin fresh and clean. Mask hydrating agent, will lock the moisture in the membrane, soften cuticles and help the skin to absorb nutrients, Mask quickly soothe the skin, eliminate fatigue and restore the skin's luster and elasticity. Pristine liquid containing plant extracts to soften skin tissue, promote skin metabolism, for dry or dehydrated skin. White Water mask can thoroughly remove dead skin cells, while having clean water and instant whitening effect, make the skin smooth and reproduce young, white and transparent.

Companies registered capital of 35 million yuan, the end of 2014 the total assets of 48.69 million yuan, including fixed assets of 37.52 million yuan. The company's existing cooperation Orange cultivation base 7043.5 acres, the company production base is located in Jiangxi County Tech Industrial Park Chu Tan industrial area, covers an area of 120 acres, it has built a standard plant 9,000 square meters, Nissan 6000 kg Orange enzymes and other liquid enzyme products. Enzyme, known as enzyme, refers to a polymer substance having biocatalytic functionality. In the catalytic reaction system an enzyme, the reactant molecules are known as substrates, enzyme substrates by catalytic conversion to another molecule. Almost all cellular activity of enzymes involved in the process are required to improve efficiency. Similar to other non-biological catalysts, enzymes chemical reactions by lowering the activation energy to accelerate the rate of the reaction, most of the enzyme catalyzed reaction rate can be increased a million times; in fact, the enzyme is to provide an activation energy needs than another low way, so that more particles to have less than the activation energy of the reaction kinetic energy, thus speeding up the reaction rate. Enzyme as a catalyst, in itself is not consumed during the reaction, it does not affect the chemical equilibrium reactions. Positive enzyme catalysis, but also a negative catalytic effect, not only to accelerate the reaction rate, but also to reduce the reaction rate. And other non-living catalysts is different, having a high degree of specificity of enzyme, only a catalytic reaction or produce a particular specific configuration.

Orange Enzyme Into Beauty Revitalizing Mask 2 Bossgoo(China)Tecgnology , https://www.cn-gangdao.com