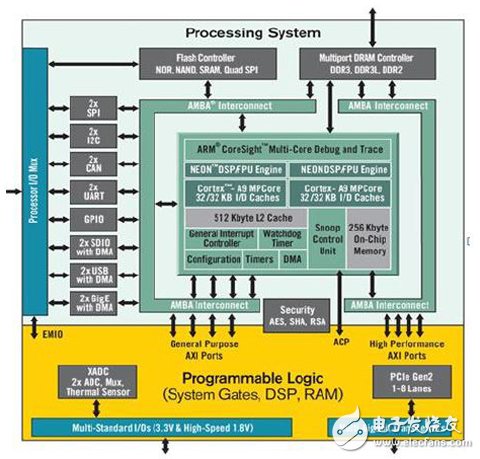

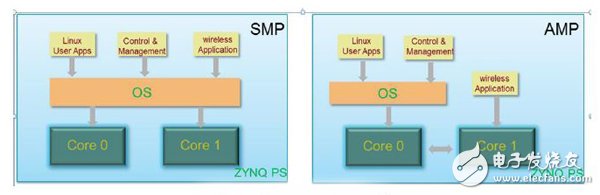

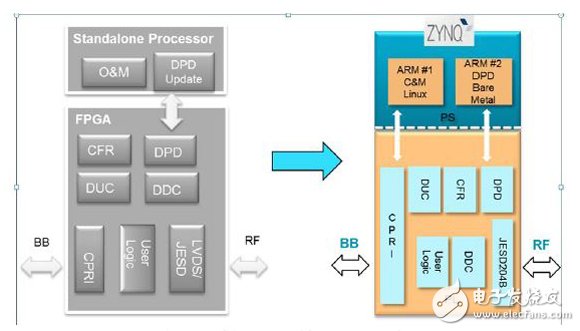

As wireless data transmissions are exploding, digital signal processing technology and radio equipment are under tremendous pressure to improve performance. At present, the global focus is on 4G LTE, and there are large-scale deployments around the world. The industry has also started early research and development of 5G networks, with the goal of increasing the data transmission capacity of 5G networks to more than 1,000 times that of 4G networks. . This emerging technology development brings new requirements for system vendors to evolving, including improving system integration and system performance, reducing system bill of materials (BOM) costs, increasing design flexibility, and accelerating time-to-market. The hardware solutions supported by traditional ASIC components, while still meeting power and cost targets, require a one-time engineering cost (NRE) and lack of flexibility, making the time-to-market of the product very slow. In response to the new demands of the market and overcoming these challenges, Xilinx has introduced the All Programmable SoC (APSoC) architecture and successfully built it into the Zynq-7000 product line. The Zynq-7000 component leverages the Xilinx APSoC architecture to deliver system-level differentiation, integration and flexibility through hardware, software and I/O programmability (Figure 1). Figure 1 Zynq-7000 All Programmable SoC Architecture Since the introduction of the Zynq-7000 component in December 2011, Xilinx has been widely used in communications, data centers, automotive, industrial, aerospace and defense. For the communications market, especially for wireless applications, the Zynq-7000 offers unique advantages: Its integrated programmable logic is highly optimized for digital signal processing; its ARM Cortex A9 processing subsystem effectively controls the control of typical wireless devices such as remote radios and wireless backhaul units. When designing wireless applications with Zynq APSoC components, you must choose an operating system that meets your application needs. There are several key factors that must be considered when targeting different wireless applications: 1. Carrier-class operational capabilities: Carrier-grade systems typically achieve 99.999% system reliability, which is the system's uptime. From the perspective of system operation, this represents support for the various features of the system, such as cold/warm restart, fault monitoring, detection and processing, and redundancy. 2. Real-time processing: Real-time not only means that the speed is "very fast", but also has a predictable response time. Remote radios have different real-time processing requirements than wireless backhaul processing. Radio signal processing tasks are arduous, so processors that support signal processing must meet stringent timing budget requirements. 3. Diagnostics: To support on-site and post-diagnosis, a large amount of performance measurement data and log data need to be collected and stored to track and manage key metrics for wireless applications such as performance measurement and statistics, CPU usage and fault monitoring, Indicators such as operating system task switching and event history. 4. Tool and Protocol Integration : Full integration of the debug and diagnostic environment, as well as specific network protocol stacks provided by some operating system vendors, helps designers develop efficient systems and maintain efficient system operations. The Zynq SoC integrates two ARM Cortex A9 cores. Software designers need to choose between SMP (Symmetric Multiprocessing Architecture) or AMP (Asymmetric Multiprocessing Architecture) multiprocessor architectures that support this ARM core. As shown in Figure 2, in an SMP system architecture, two or more identical processors share resources in a single operating system instance. Figure 2 Comparison of SMP and AMP In theory, this architecture treats all processors equally in the same operating system instance. Conversely, with or without an operating system instance and a processor that do not know each other, the AMP architecture will treat different processors differently, while the core without the operating system may execute a "bare metal" The microprogram code of the instance. SMP usually provides a unified operating system platform for higher-order applications. Software architects don't have to worry about sharing resources and cross-trip communication between the two cores when building applications on the operating system. In addition, the performance of SMPs can impact time-critical wireless applications. Compared to SMP, AMP's lightweight software with operating system instances has almost no consumption problems, but requires elaborate software design to achieve processor resource sharing and communication between processors. The Zynq APSoC component enables the efficient deployment of a wide range of important wireless applications, including radio and wireless backhaul. Each wireless application has different performance requirements and requires the operating system to support different features. The radio application is a good example of a Zynq application because Zynq provides a complete software and hardware integration solution that includes all digital front-end processing capabilities. The radio digital front-end application is a major part of a typical remote radio head-end device (RRH) in a 4G wireless network. The processing requirements of this application can be divided into signal processing and control processing. In the field of signal processing, Zynq can be built to high sample rate filters for digital up/down conversion, crest factor suppression (CFR) and digital predistortion (DPD). However, DPD is a special case that requires the simultaneous use of Zynq's PS and PL. DPD processing can be subdivided into high speed data paths and update paths. The update path is used to periodically update the coefficients of the filter bank, making it ideal for ARM Cortex A9 cores. In general, coefficient updates must be completed in milliseconds to tens of milliseconds. Due to the arithmetic complexity of the calculations, the A9 core and the embedded NEON SIMD vector arithmetic unit can be used to cope with the required high performance. In addition, Zynq PL provides hardware acceleration for a variety of functions that require a large number of processor frequency cycles, so Zynq PL, ARM A9 cores, and NEON co-processors can work together. Radio control processing is typically used for initial radio calibration, configuration, warning, scheduling, and termination of messages from the network. Such operations typically do not require high performance in radio applications, so they can be easily managed using a single ARM A9 core built into the Zynq component. Choosing the right architecture to support DPD applications and control processing applications is important because the right architecture determines overall performance, reliability, and ease of maintenance. The AMP mode is a general architecture for radio applications. In this mode, a complete ARM core can be provided for bare DPD processing in bare metal mode, thus providing more computational margin to meet the time required for various DPD coefficient updates. The second ARM A9 core controlled by the operating system can perform all applications such as control and OAM. In this architecture, since the operating system can only control one of the two ARM cores, it is necessary to establish a channel between the two independent cores, for example, using OCM (On Chip Memory) or Shared memory. This is especially important for certain important control applications, such as those used to monitor the condition of the DPD module. This inter-trip communication (IPC) solution does not have a standard to follow, but must be developed separately in the AMP mode. The SMP architecture is very simple and straightforward, that is, using a single operating system instance to control two ARM cores simultaneously, thus controlling all applications. IPC, debug, and support toolchains all operate under the same operating system. In order to ensure that DPD applications have their own resources, special technologies such as Core Affinity and Interrupt Masking can be used in software applications. In the previous case, the DPD application was only executed on one core, that is, the DPD application did not share resources with other jobs except for operating system scheduler consumption. In the latter case, in addition to the execution tasks required for the DPD application, various interrupt services are directly transferred to the second core. As a result, DPD applications can make full use of all resources. Thus, Zynq APSoC is an ideal platform to support AMP or SMP architecture. As shown in Figure 3, Zynq integrates two ARM core processors, a 12.5Gb/s sequencer/serializer (SerDes), a more reliable 500MHz+ DSP, and provides complete digital front-end functions such as DPD. CFR, DUC/DDC and CPRI/JESD interfaces. This solution simplifies PCB design by eliminating the need to interface between the processor and individual FPGA components. The single-chip integration solution from the stand-alone multi-chip solution to the Zynq platform is fairly straightforward. Xilinx offers a comprehensive range of hardware and software solutions, including digital signal processing IP libraries for DUC, DDC, CFR and DPD, enabling the multi-chip solution to be smoothly transferred to the Zynq platform. In addition, Xilinx provides support for a variety of operating system solutions, including component drivers, boot loaders, BSP samples, and commonly used tools. When the design is successfully transferred to the Zynq platform, system performance can be significantly improved, saving overall power consumption and reducing bill of materials (BOM) costs. Figure 3: Moving from a standalone solution to a Zynq solution Above, we explored the main considerations for choosing an operating system for wireless applications, the architecture of the wireless application, and the considerations in which AMP and SMP are compared, as well as applications that can directly use Xilinx Zynq 7000 components. In summary, Xilinx's high-end components enable infrastructure equipment designers to achieve hardware and software programmability while improving performance and system integration, reducing bill of materials (BOM) total cost and overall system power consumption. And achieve high reliability and accelerate time-to-market. Designers can now not only speed up the development of their equipment, but they can continue to provide field updates after the device is deployed, eliminating the risks associated with components such as ASSPs and ASICs. All in one pc 23.8 inch, all in one pc i5 8gb ram, all in one desktop intel core i5, pc all in one 24 inch Guangdong Elieken Electronic Technology Co.,Ltd. , https://www.elieken.com