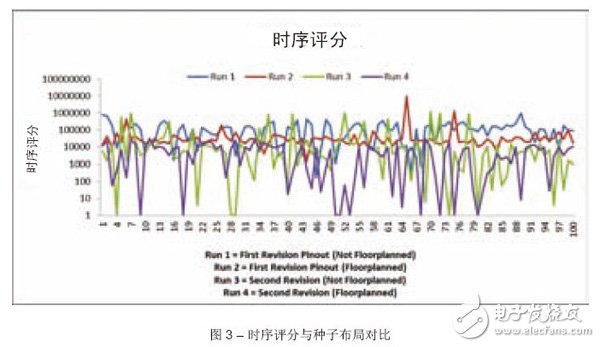

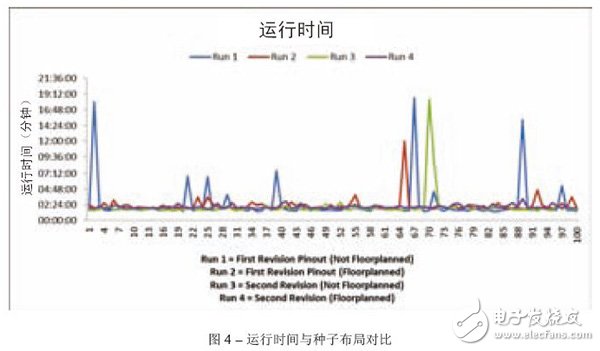

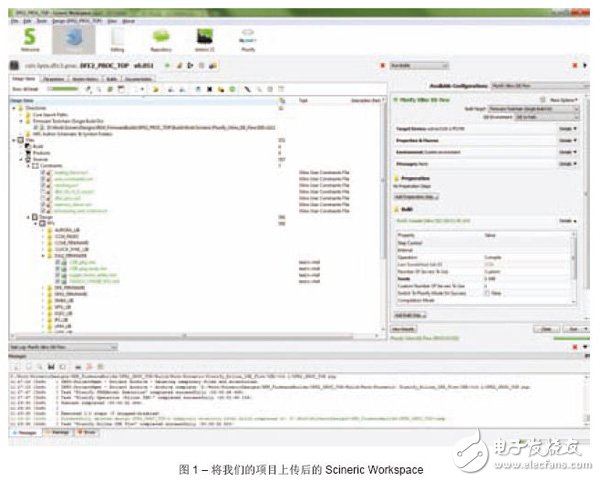

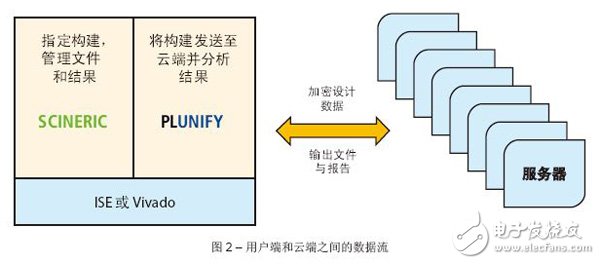

Engineers from the Council for Scientific and Industrial Research (CSIR) and Plunify tell you how they use cloud computing to analyze implementation options and user constraints for large Virtex-6 designs. As FPGA devices increase in size and their internal design density increases, timing closure faces unprecedented challenges. As various implementation tools compete to meet this higher complexity requirement, it takes longer and longer to shift different implementations into mass production [1]. To speed things up, some designers hope to compare the effects of using different implementation options and user-constrained decisions through cloud computing. Recently, we completed such an analysis process at the Scientific and Industrial Research Council (CSIR) in South Africa. We used Plunify's cloud acceleration chip design method to find the parameters that provide the shortest implementation runtime and the best timing score for our design. Before delving into the details of our analysis and the tools we use, let's take a look at some background information. Development Board Upgrade In a recent project, we needed to upgrade the existing development board by replacing the remaining Xilinx Virtex-5 FPGA with a new generation of Virtex-6 devices. The first development board has several major problems, the most important of which is that the pin is not optimal for the target application, and the device size is too small to meet the system requirements. We already have most of the RTL code needed to run a new development board, so we have an absolute advantage in this area to analyze the decisions made during the pin assignment phase of PCB schematic design. Since the FPGA design implementation takes a long time to run, we have to limit the number of builds performed during the PCB design phase to make decisions. During the hardware testing phase of the design, we added some features that were not available on the original Virtex-5 development board. Unsurprisingly, this created more work for the place and route tool, so we did a detailed layout planning exercise and completed a lot of runs to find the best placement seed. We decided to use Plunify's cloud implementation service to manage the large amount of operations we need. FPGAAccel is a software application programming interface (API) that helps you define, assign, and execute FPGA synthesis and place and route builds simultaneously on a remote server. Four Constraint Sets Due to the processing capabilities provided by the Plunify service, we decided to analyze our final design with four different constraint sets. The first two constraint sets share the same pin, the first constraint set does not include layout planning, and the second includes detailed layout planning. The pins we chose for these two constraint sets were able to reproduce the consequences of improper pin assignments we encountered on the first development board. The other two constraint sets use the pins of the devices on the new development board; similarly, one of the constraint sets does not include layout planning, and the other includes detailed layout planning. We need to use these constraint sets to verify that changes to the FPGA pins really affect timing closure, and that changing the seed layout on the first version of the board alone is not enough to meet the timing specifications. We run 100 builds for each constraint set and use different seed layouts from 1-100. Tools Used For FPGA design software, we use the Xilinx ISE® Design Suite Logic Version 14.4 to complete the tasks in the existing workflow in the designer's local environment; in the cloud, we use it to complete synthesis and place and route. task. At the front end, CSIR's Scineric Workspace (see Figure 1) is a new, fast, lightweight integrated development environment for FPGA design management based on IP-XACT. The tool uses a new "file manager" approach to design management, helping designers to preview every aspect of the design at any time. It has a design fusion feature that integrates Scineric into existing workflows to provide a specific design environment that users prefer. We can use the Scineric Workspace graphical interface loaded into the ISE project to configure, submit, and retrieve builds from the cloud. However, this front end is not a hard requirement; the Plunify client can be smoothly integrated into ISE and Vivado® processes. On the back end, Plunify's FPGA-Accel client is a software API that allows engineers to simultaneously define, assign, and execute FPGA synthesis and place and route builds on remote servers and analyze the results after all builds have been completed. In this example, we use a cloud computing server farm to process 400 builds. Scineric Workspace supports a variety of configurations including the FPGAAccel client. Figure 2 shows how designers use these tools at work. The specific process is as follows: Scineric Workspace allows users to import designs from a variety of sources, including Xilinx ISE and Vivado projects and IP-XACT component definition files. Each design can have multiple build configurations, including configurations that allow you to define Plunify experiments that can then be uploaded to Plunify. 4. Upload the build request. In the cloud, Plunify software generates the required builds, allocates 400 servers and runs ISE to synthesize and place and route different experiments on each server. 5. Once the build is complete, you will receive an email notification. Completing 400 builds in parallel We used the results of these 400 builds for multiple standard tests, including average run time, number of non-routable solutions, and timing scores for cabling solutions, which is also the most important. Figure 3 shows the results of the time series scoring of the four constraint sets. Through our four constraint sets, we have again demonstrated that the invalid pins of the target application can seriously affect the timing score of the design. In addition, we can determine the best seed layout for this design, and in this particular case, we realized that the implementation tool performed best without being guided by the layout plan. Figure 4 shows the runtime of the four constraint sets. In the past, such a run took more than 30 days to complete, but with what we said, we only got results and analysis in one day. Another advantage of this approach is that all data is managed by Plunify, and this advantage is only discovered when we see how much data was generated in these 400 runs (200 gigabytes). We only need to download the specific running results that we are interested in. Optimal Timing Score Timing closure is an important part of any FPGA design, and we have shown that many parameters have an impact on your timing score. With new tools and cloud computing technology, our analysis of these impacts is significantly faster than ever. We were able to determine which constraint set and seed layout would give us the best timing score for our design. By using the best parameters, we can continue with the next phase of system development because our builds meet their timing specifications. Gaming Power,High Efficiency Game Power,Game Mute Version Computer Power,Pc 850W Game Power Boluo Xurong Electronics Co., Ltd. , https://www.greenleaf-pc.com

1. Open Scineric Workspace.

2. Import the ISE project.

3. Limit 100 experiments for each ISE project.

The Plunify plugin first authenticates the identity of the designer and then encrypts all the design files in the ISE project. Next, it securely transfers the file to the remote server farm along with the build parameters.

6. Log in to view the report with your work ID

7. Repeat the above steps for each ISE project.